EN: This Datasheet is presented by the manufacturer.

Please visit our website for pricing and availability at www.hestore.hu.

# 20W BRIDGE AMPLIFIER FOR CAR RADIO

**High output power :**  $P_O = 10 + 10 \text{ W}@R_L = 2\Omega$ , d = 10%;  $P_O = 20\text{W}@R_L = 4\Omega$ , d = 1%.

**High reliability** of the chip and package with additional complete safety during operation thanks to protection against:

- OUTPUT DC AND AC SHORT CIRCUIT TO GROUND

- OVERRATING CHIP TEMPERATURE

- LOAD DUMP VOLTAGE SURGE

- FORTUITOUS OPEN GROUND

- VERY INDUCTIVE LOADS

**Flexibility in use:** bridge or stereo booster amplifiers with or without boostrap and with programmable gain and bandwidth.

**Space and cost saving:** very low number of external components, very simple mounting system with no electrical isolation between the package and the heatsink (one screw only).

In addition, the circuit offers **loudspeaker protection** during short circuit for one wire to ground.

## **DESCRIPTION**

The TDA2005 is class B dual audio power amplifier in MULTIWATT® package specifically designed for car radio application : **power booster amplifiers** are easily designed using this device that provides a high current capability (up to 3.5 A) and that can drive very low impedance loads (down to  $1.6\Omega$  in

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                            | Parameter                                       | Value       | Unit |

|-----------------------------------|-------------------------------------------------|-------------|------|

| Vs                                | Operating Supply Voltage                        | 18          | V    |

| Vs                                | DC Supply Voltage                               | 28          | V    |

| Vs                                | Peak Supply Voltage (for 50 ms)                 | 40          | V    |

| I <sub>o</sub> (*)                | Output Peak Current (non repetitive t = 0.1 ms) | 4.5         | А    |

| I <sub>o</sub> (*)                | Output Peak Current (repetitive f ≥ 10 Hz)      | 3.5         | А    |

| P <sub>tot</sub>                  | Power Dissipation at T <sub>case</sub> = 60 °C  | 30          | W    |

| T <sub>stg</sub> , T <sub>j</sub> | Storage and Junction Temperature                | - 40 to 150 | °C   |

<sup>(\*)</sup> The max. output current is internally limited.

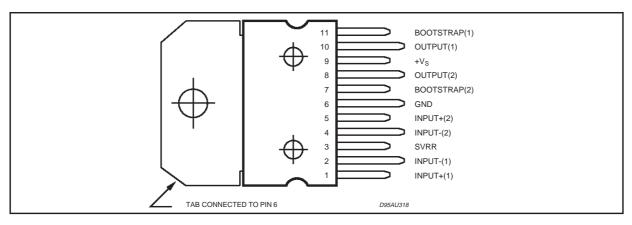

#### **PIN CONNECTION**

October 1998 1/20

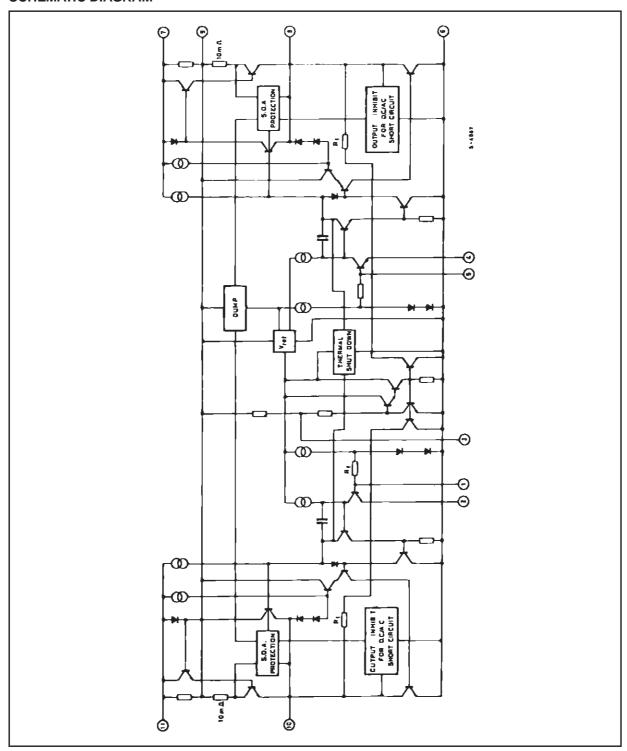

## **SCHEMATIC DIAGRAM**

# THERMAL DATA

| Symbol                 | Parameter                             | Value | Unit |

|------------------------|---------------------------------------|-------|------|

| R <sub>th j-case</sub> | Thermal Resistance Junction-case Max. | 3     | °C/W |

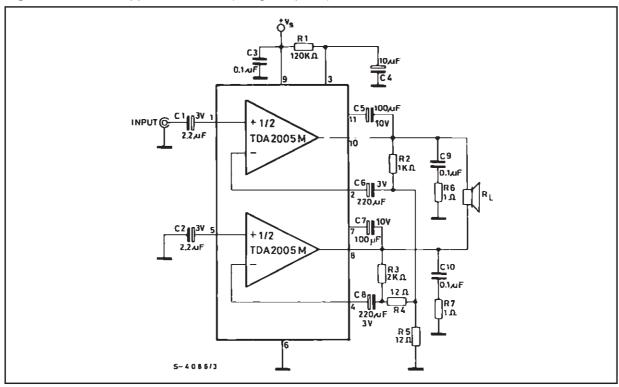

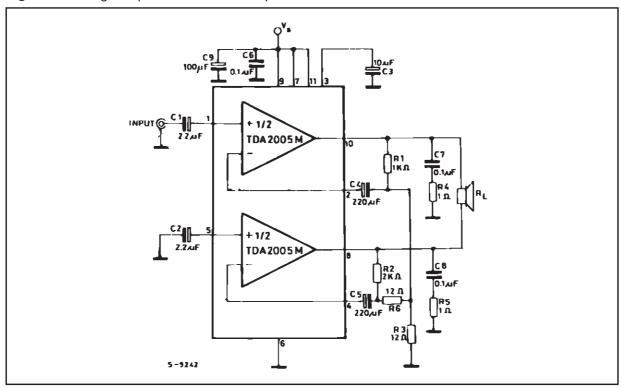

# **BRIDGE AMPLIFIER APPLICATION (TDA2005M)**

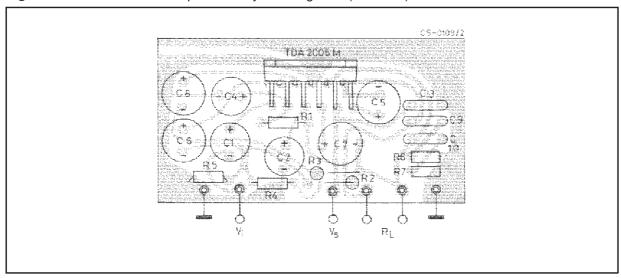

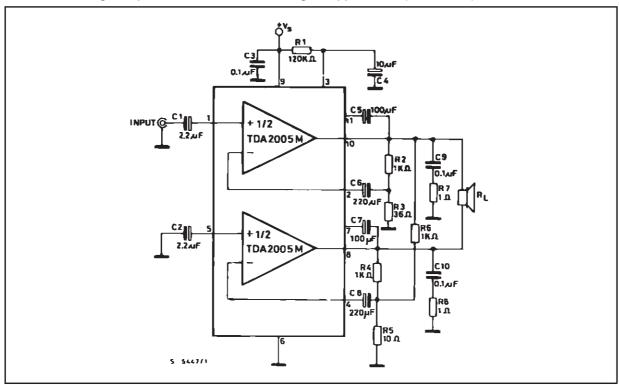

Figure 1: Test and Application Circuit (Bridge amplifier)

Figure 2: P.C. Board and Components Layout of Figure 1 (1:1 scale)

**ELECTRICAL CHARACTERISTICS** (refer to the **Bridge** application circuit,  $T_{amb} = 25^{\circ}C$ ,  $G_{V} = 50 dB$ ,  $R_{th (heatsink)} = 4^{\circ}C/W$ , unless otherwise specified)

| Symbol                     | Parameter                                                                                     | Test Conditions                                                                                                                                                                                                                                                                                                        | Min.           | Тур.           | Max.       | Unit        |

|----------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|------------|-------------|

| Vs                         | Supply Voltage                                                                                |                                                                                                                                                                                                                                                                                                                        | 8              |                | 18         | V           |

| V <sub>os</sub>            | Output Offset Voltage (1) (between pin 8 and pin 10)                                          | $V_s = 14.4V$<br>$V_s = 13.2V$                                                                                                                                                                                                                                                                                         |                |                | 150<br>150 | mV<br>mV    |

| I <sub>d</sub>             | Total Quiescent Drain Current                                                                 | $V_s = 14.4V$ $R_L = 4\Omega$ $V_s = 13.2V$ $R_L = 3.2\Omega$                                                                                                                                                                                                                                                          |                | 75<br>70       | 150<br>160 | mA<br>mA    |

| P <sub>o</sub>             | Output Power                                                                                  |                                                                                                                                                                                                                                                                                                                        | 18<br>20<br>17 | 20<br>22<br>19 |            | W           |

| d                          | Distortion                                                                                    | $ \begin{cases} \text{f} = 1 \text{kHz} \\ \text{V}_{\text{s}} = 14.4 \text{V} & \text{R}_{\text{L}} = 4 \Omega \\ \text{P}_{\text{o}} = 50 \text{mW to } 15 \text{W} \\ \text{V}_{\text{s}} = 13.2 \text{V} & \text{R}_{\text{L}} = 3.2 \Omega \\ \text{P}_{\text{o}} = 50 \text{mW to } 13 \text{W} \\ \end{cases} $ |                |                | 1          | %<br>%      |

| Vi                         | Input Sensitivity                                                                             |                                                                                                                                                                                                                                                                                                                        |                | 9<br>8         |            | mV<br>mV    |

| Ri                         | Input Resistance                                                                              | f = 1kHz                                                                                                                                                                                                                                                                                                               | 70             |                |            | kΩ          |

| f∟                         | Low Frequency Roll Off (- 3dB)                                                                | $R_L = 3.2\Omega$                                                                                                                                                                                                                                                                                                      |                |                | 40         | Hz          |

| f <sub>H</sub>             | High Frequency Roll Off (- 3dB)                                                               | $R_L = 3.2\Omega$                                                                                                                                                                                                                                                                                                      | 20             |                |            | kHz         |

| G√                         | Closed Loop Voltage Gain                                                                      | f = 1kHz                                                                                                                                                                                                                                                                                                               |                | 50             |            | dB          |

| e <sub>N</sub>             | Total Input Noise Voltage                                                                     | $R_g = 10k\Omega$ (2)                                                                                                                                                                                                                                                                                                  |                | 3              | 10         | μV          |

| SVR                        | Supply Voltage Rejection                                                                      | $\begin{aligned} R_g &= 10k\Omega, \ C_4 = 10\mu F \\ f_{ripple} &= 100Hz, \ V_{ripple} = 0.5V \end{aligned}$                                                                                                                                                                                                          | 45             | 55             |            | dB          |

| η                          | Efficiency                                                                                    | $\begin{array}{l} V_{s}=14.4V,f=1\text{kHz}\\ P_{o}=20W & R_{L}=4\Omega\\ P_{o}=22W & R_{L}=3.2\Omega\\ V_{s}=13.2V,f=1\text{kHz}\\ P_{o}=19W & R_{L}=3.2\Omega \end{array}$                                                                                                                                           |                | 60<br>60<br>58 |            | %<br>%<br>% |

| Tj                         | Thermal Shut-down Junction<br>Temperature                                                     | $\begin{aligned} &V_s = 14.4V, \ R_L = 4\Omega \\ &f = 1 \text{kHz}, \ P_{tot} = 13W \end{aligned}$                                                                                                                                                                                                                    |                | 145            |            | °C          |

| V <sub>OSH</sub> Notes: 1. | Output Voltage with one Side of the Speakershierled to ground Bandwith Filter: 22Hz to 22kHz. | $ \begin{array}{lll} V_s = 14.4V & R_L = 4\Omega \\ V_s = 13.2V & R_L = 3.2\Omega \end{array} $                                                                                                                                                                                                                        |                |                | 2          | V           |

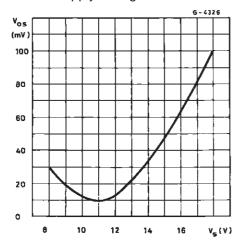

Output Offset Voltage versus Figure 3: Supply Voltage

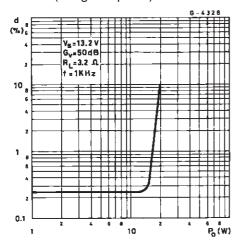

Distortion versus Output Power Figure 4: (bridge amplifier)

Figure 5: Distortion versus Output Power (bridge amplifier)

# **BRIDGE AMPLIFIER DESIGN**

The following consideraions can be useful when designing a bridge amplifier.

|                    | Parameter                              | Single Ended                                            | Bridge                                 |

|--------------------|----------------------------------------|---------------------------------------------------------|----------------------------------------|

| V <sub>o max</sub> | Peak Output Voltage (before clipping)  | $\frac{1}{2}$ (V <sub>s</sub> - 2 V <sub>CE sat</sub> ) | V <sub>s</sub> – 2 V <sub>CE sat</sub> |

| I <sub>o max</sub> | Peak Output Current (before clippling) | $\frac{1}{2} \frac{V_S - 2 V_{CE \ sat}}{R_L}$          | $\frac{V_{S}-2\ V_{CE\ sat}}{R_{L}}$   |

| P <sub>o max</sub> | RMS Output Power (before clipping)     | $\frac{1}{4} \frac{(V_S - 2 V_{CE sat})^2}{2 R_L}$      | $\frac{(V_S - 2 V_{CE sat})^2}{2 R_L}$ |

Where:  $V_{CE\ sat}$  = output transistors saturation voltage

Vs = allowable supply voltage R<sub>L</sub>= load impedance

Voltage and current swings are twice for a bridge amplifier in comparison with single ended amplifier. In order words, with the same R<sub>L</sub> the bridge configuration can deliver an output power that is four times the output power of a single ended amplifier, while, with the same max output current the bridge configuration can deliver an output power that is twice the output power of a single ended amplifier. Core must be taken when selecting Vs and R<sub>L</sub> in order to avoid an output peak current above the absolute maximum rating.

From the expression for  $I_{Omax}$ , assuming  $V_S = 14.4V$  and  $V_{CE\ sat} = 2V$ , the minimum load that can be driven by TDA2005 in bridge configuration is :

$$R_{L\,min} = \frac{V_S - 2\;V_{CEsat}}{I_{O\;max}} = \frac{14.4 - 4}{3.5} = 2.97\Omega$$

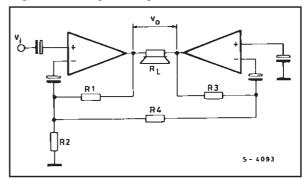

The voltage gain of the bridge configuration is given by (see Figure 34):

$$G_V = \frac{V_0}{V_1} = 1 \, + \frac{R_1}{\left(\frac{R_2 \cdot R_4}{R_2 + R_4}\right)} + \frac{R_3}{R_4}$$

For sufficiently high gains (40 to 50dB) it is possible to put  $R_2 = R_4$  and  $R_3 = 2 R_1$ , simplifying the formula in :

$$Gv = 4 \frac{R_1}{R_2}$$

| G <sub>√</sub> (dB) | R <sub>1</sub> (Ω) | $R_2 = R_4 (\Omega)$ | R <sub>3</sub> (Ω) |

|---------------------|--------------------|----------------------|--------------------|

| 40                  | 1000               | 39                   | 2000               |

| 50                  | 1000               | 12                   | 2000               |

Figure 6: Bridge Configuration

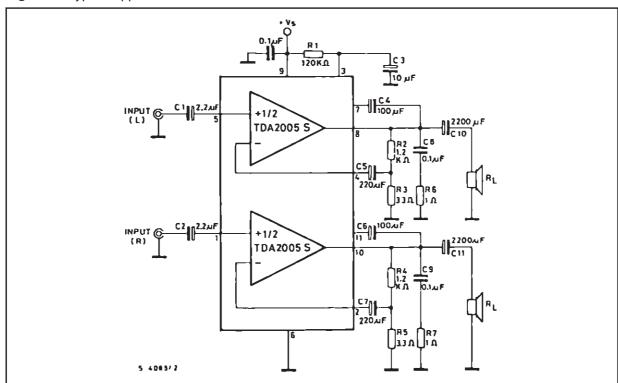

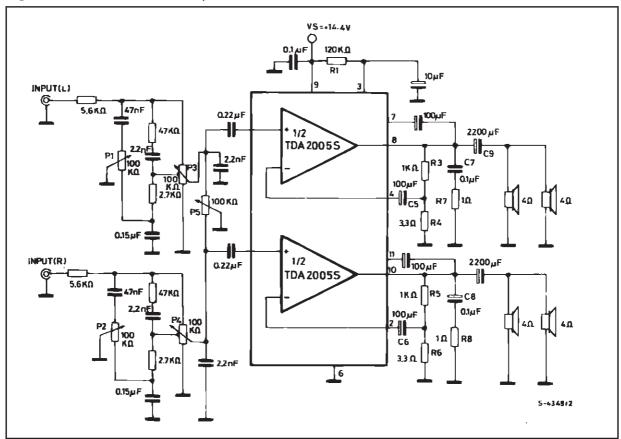

## STEREO AMPLIFIER APPLICATION (TDA2005S)

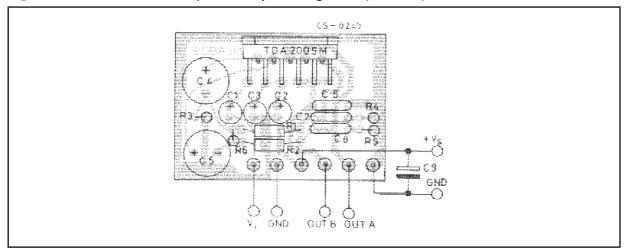

Figure 7: Typical Application Circuit

5

**ELECTRICAL CHARACTERISTICS** (refer to the **Stereo** application circuit,  $T_{amb} = 25^{\circ}C$ ,  $G_{V} = 50 dB$ ,  $R_{th \, (heatsink)} = 4^{\circ}C/W$ , unless otherwwise specified)

| Symbol         | Parameter                       | Test Conditions                                                                                                                                                                                                                                                                                                                       | Min.                        | Тур.                              | Max.             | Unit             |

|----------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------|------------------|------------------|

| Vs             | Supply Voltage                  |                                                                                                                                                                                                                                                                                                                                       | 8                           |                                   | 18               | V                |

| Vo             | Quiescent Output Voltage        | $V_s = 14.4V$<br>$V_s = 13.2V$                                                                                                                                                                                                                                                                                                        | 6.6<br>6                    | 7.2<br>6.6                        | 7.8<br>7.2       | V                |

| I <sub>d</sub> | Total Quiescent Drain Current   | $V_s = 14.4V$<br>$V_s = 13.2V$                                                                                                                                                                                                                                                                                                        |                             | 65<br>62                          | 120<br>120       | mA<br>mA         |

| Po             | Output Power (each channel)     | $ f = 1 \text{kHz, } d = 10\% \\ V_s = 14.4 \text{V} & R_L = 4 \Omega \\ R_L = 3.2 \Omega \\ R_L = 2 \Omega \\ R_L = 1.6 \Omega \\ V_s = 13.2 \text{V} & R_L = 3.2 \Omega \\ R_L = 1.6 \Omega \\ V_s = 16 \text{V} & R_L = 2 \Omega \\ $                                                                                              | 6<br>7<br>9<br>10<br>6<br>9 | 6.5<br>8<br>10<br>11<br>6.5<br>10 |                  | W                |

| d              | Distortion (each channel)       | $\begin{array}{lll} f = 1 \text{kHz} \\ V_s = 14.4 \text{V} & R_L = 4 \Omega \\ P_o = 50 \text{mW to 4W} \\ V_s = 14.4 \text{V} & R_L = 2 \Omega \\ P_o = 50 \text{mW to 6W} \\ V_s = 13.2 \text{V} & R_L = 3.2 \Omega \\ P_o = 50 \text{mW to 3W} \\ V_s = 13.2 \text{V} & R_L = 1.6 \Omega \\ P_o = 40 \text{mW to 6W} \end{array}$ |                             | 0.2<br>0.3<br>0.2<br>0.3          | 1<br>1<br>1<br>1 | %<br>%<br>%<br>% |

| СТ             | Cross Talk (1)                  | $\label{eq:controller} \begin{array}{l} V_{s}=14.4V,\ V_{o}=4V_{RMS}\\ R_{L}=4\Omega,\ R_{g}=5k\Omega\\ f=1kHz\\ f=10kHz \end{array}$                                                                                                                                                                                                 |                             | 60<br>45                          |                  | dB               |

| Vi             | Input Saturation Voltage        |                                                                                                                                                                                                                                                                                                                                       | 300                         |                                   |                  | mV               |

| Vi             | Input Sensitivity               | $f = 1kHz, P_o = 1W$ $R_L = 4\Omega$ $R_L = 3.2\Omega$                                                                                                                                                                                                                                                                                |                             | 6<br>5.5                          |                  | mV               |

| Ri             | Input Resistance                | f = 1kHz                                                                                                                                                                                                                                                                                                                              | 70                          | 200                               |                  | kΩ               |

| fL             | Low Frequency Roll Off (-3dB)   | $R_L = 2\Omega$                                                                                                                                                                                                                                                                                                                       |                             |                                   | 50               | Hz               |

| f <sub>H</sub> | High Frequency Roll Off (- 3dB) | $R_L = 2\Omega$                                                                                                                                                                                                                                                                                                                       | 15                          |                                   |                  | kHz              |

| Gv             | Voltage Gain (open loop)        | f = 1kHz                                                                                                                                                                                                                                                                                                                              |                             | 90                                |                  | dB               |

| G <sub>v</sub> | Voltage Gain (closed loop)      | f = 1kHz                                                                                                                                                                                                                                                                                                                              | 48                          | 50                                | 51               | dB               |

| $\Delta$ $G_v$ | Closed Loop Gain Matching       |                                                                                                                                                                                                                                                                                                                                       |                             | 0.5                               |                  | dB               |

| e <sub>N</sub> | Total Input Noise Voltage       | $R_g = 10k\Omega$ (2)                                                                                                                                                                                                                                                                                                                 |                             | 1.5                               | 5                | μV               |

| SVR            | Supply Voltage Rejection        | $\begin{array}{c} R_g = 10k\Omega,\ C_3 = 10\mu F\\ f_{ripple} = 100Hz,\ V_{ripple} = 0.5V \end{array}$                                                                                                                                                                                                                               | 35                          | 45                                |                  | dB               |

| η              | Efficiency                      | $\begin{array}{c} V_{s}=14.4V,f=1kHz\\ P_{o}=6.5W & R_{L}=4\Omega\\ P_{o}=10W & R_{L}=2\Omega\\ V_{s}=13.2V,f=1kHz\\ P_{o}=6.5W & R_{L}=3.2\Omega\\ P_{o}=100W & R_{L}=1.6\Omega \end{array}$                                                                                                                                         |                             | 70<br>60<br>70<br>60              |                  | %<br>%<br>%      |

Notes: 1. For TDA2005M only 2. Bandwith Filter: 22Hz to 22kHz.

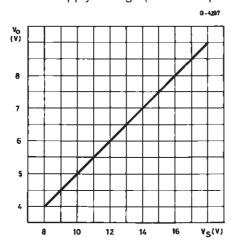

Figure 8: Quiescent Output Voltage versus Supply Voltage (Stereo amplifier)

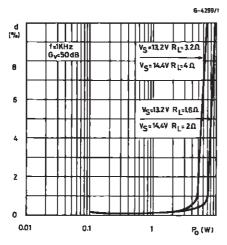

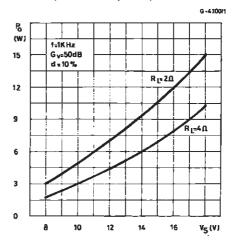

Figure 10: Distortion versus Output Power (Stereo amplifier)

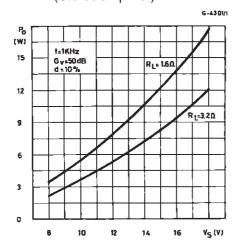

Figure 12: Output Power versus Supply Voltage (Stereo amplifier)

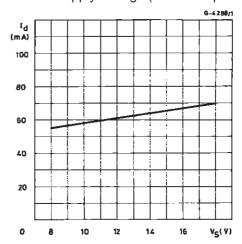

**Figure 9 :** Quiescent Drain Current versus Supply Voltage (Stereo amplifier)

Figure 11: Output Power versus Supply Voltage (Stereo amplifier)

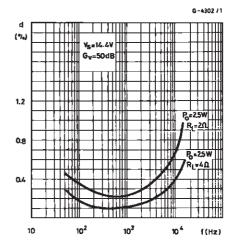

Figure 13: Distortion versus Frequency (Stereo amplifier)

57

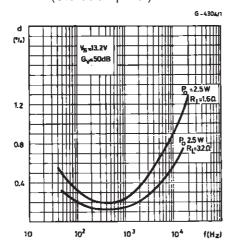

Figure 14: Distortion versus Frequency (Stereo amplifier)

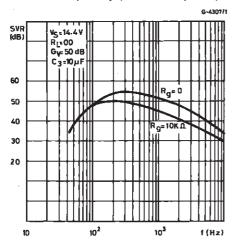

Figure 16: Supply Voltage Rejection versus Frequency (Stereo amplifier)

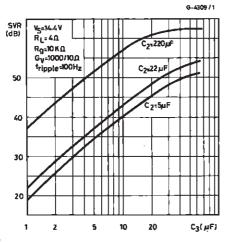

Figure 18: Supply Voltage Rejection versus C2 and C3 (Stereo amplifier)

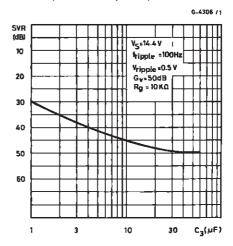

Figure 15: Supply Voltage Rejection versus C3 (Stereo amplifier)

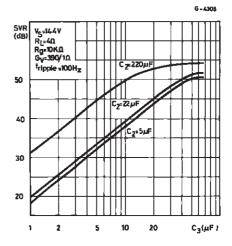

Figure 17: Supply Voltage Rejection versus C2 and C3 (Stereo amplifier)

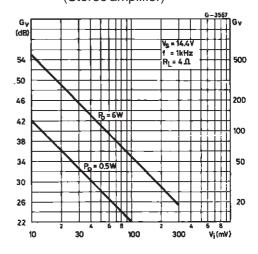

Figure 19: Gain versus Input Sensitivity (Stereo amplifier)

4

Figure 20: Gain versus Input Sensitivity (Stereo amplifier)

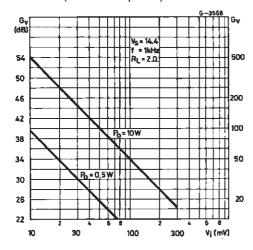

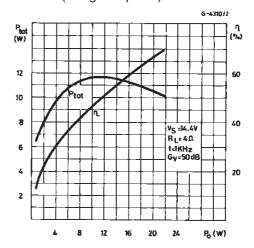

Figure 22: Total Power Dissipation and Efficiency versus Output Power (Stereo amplifier)

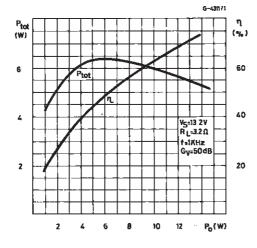

Figure 21: Total Power Dissipation and Efficiency versus Output Power (Bridge amplifier)

## **APPLICATION SUGGESTION**

The recommended values of the components are those shown on Bridge application circuit of Figure 1. Different values can be used; the following table can help the designer.

| Comp.                            | Recom.<br>Value | Purpose                                                       | Larger Than                                                     | Smaller Than                                                              |

|----------------------------------|-----------------|---------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------|

| R <sub>1</sub>                   | 120 kΩ          | Optimization of the Output<br>Symmetry                        | Smaller P <sub>o max</sub>                                      | Smaller P <sub>o max</sub>                                                |

| R <sub>2</sub>                   | 1kΩ             |                                                               |                                                                 |                                                                           |

| R <sub>3</sub>                   | 2 kΩ            |                                                               |                                                                 |                                                                           |

| R <sub>4</sub> , R <sub>5</sub>  | 12 Ω            | Closed Loop Gain Setting (see<br>Bridge Amplifier Design) (*) |                                                                 |                                                                           |

| R <sub>6</sub> , R <sub>7</sub>  | 1 Ω             | Frequency Stability                                           | Danger of Oscillation at High<br>Frequency with Inductive Loads |                                                                           |

| C <sub>1</sub>                   | 2.2 μF          | Input DC Decoupling                                           |                                                                 |                                                                           |

| C <sub>2</sub>                   | 2.2 μF          | Optimization of Turn on Pop and Turn on Delay                 | High Turn on Delay                                              | Higher Turn on Pop, Higher<br>Low Frequency Cut-off,<br>Increase of Noise |

| C <sub>3</sub>                   | 0.1 μF          | Supply by Pass                                                |                                                                 | Danger of Oscillation                                                     |

| C <sub>4</sub>                   | 10 μF           | Ripple Rejection                                              | Increase of SVR, Increase of the Switch-on Time                 | Degradation of SVR.                                                       |

| C <sub>5</sub> , C <sub>7</sub>  | 100 μF          | Bootstrapping                                                 |                                                                 | Increase of Distortion at low Frequency                                   |

| C <sub>6</sub> , C <sub>8</sub>  | 220 μF          | Feedback Input DC Decoupling,<br>Low Frequency Cut-off        |                                                                 | Higher Low Frequency<br>Cut-off                                           |

| C <sub>9</sub> , C <sub>10</sub> | 0.1 μF          | Frequency Stability                                           |                                                                 | Danger of Oscillation                                                     |

<sup>(\*)</sup> The closed loop gain must be higher than 32dB.

## **APPLICATION INFORMATION**

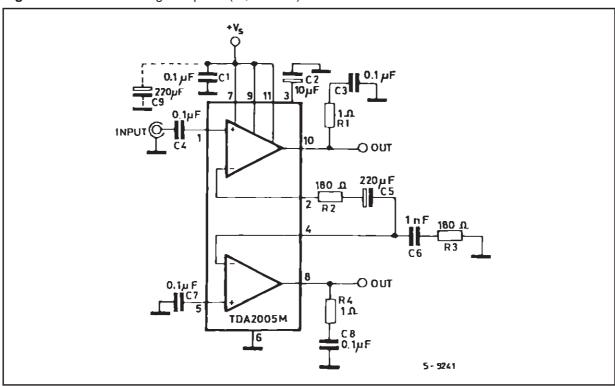

Figure 23 : Bridge Amplifier without Boostrap

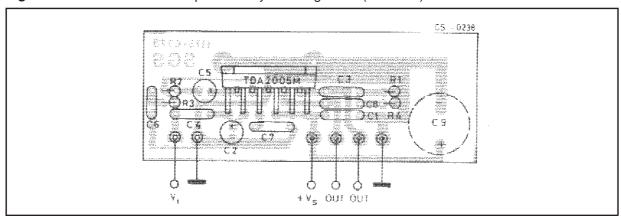

Figure 24: P.C. Board and Components Layout of Figure 23 (1:1 scale)

**Figure 25**: Low Cost Bridge Amplifier ( $G_V = 42dB$ )

Figure 26: P.C. Board and Components Layout of Figure 25 (1:1 scale)

Figure 27: 10 + 10 W Stereo Amplifier with Tone Balance and Loudness Control

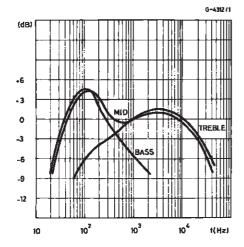

Figure 28: Tone Control Response (circuit of Figure 29)

57

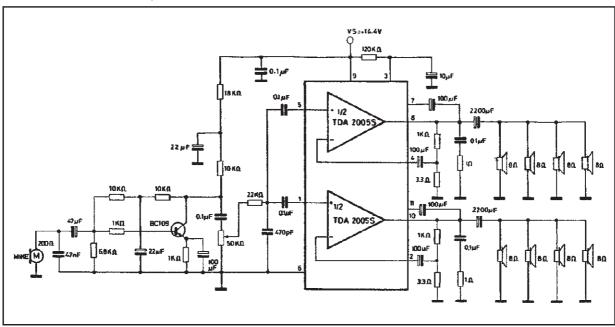

Figure 29: 20W Bus Amplifier

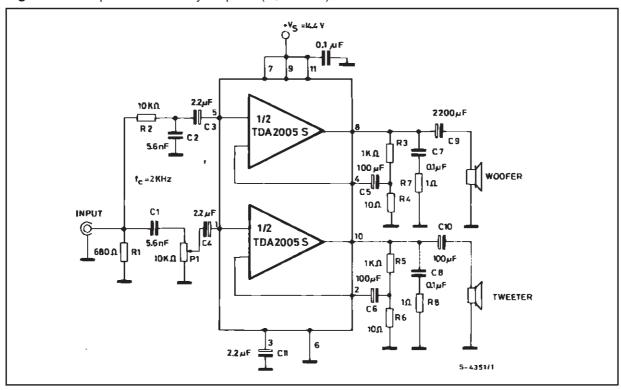

Figure 30 : Simple 20W Two Way Amplifier (Fc = 2kHz)

Figure 31 : Bridge Amplifier Circuit suited for Low-gain Applications ( $G_V = 34dB$ )

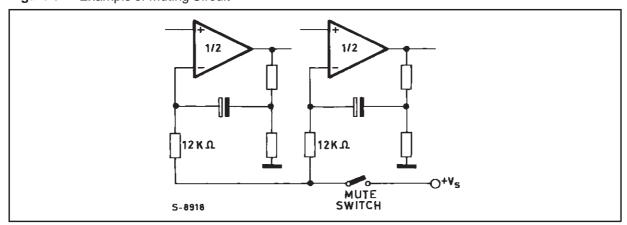

Figure 32: Example of Muting Circuit

#### **BUILT-IN PROTECTION SYSTEMS**

#### **Load Dump Voltage Surge**

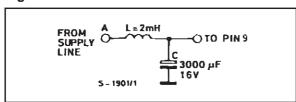

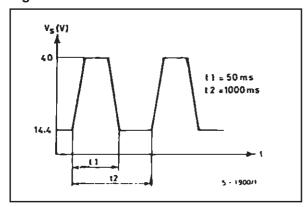

The TDA2005 has a circuit which enables it to withstanda voltage pulse train, on Pin 9, of the type shown in Figure 34.

If the supply voltage peaks to more than 40V, then an LC filter must be inserted between the supply and pin 9, in order to assure that the pulses at pin 9 will be held withing the limits shown.

A suggestedLC network is shown in Figure 33. With this network, a train of pulses with amplitude up to 120V and width of 2ms can be applied at point A. This type of protection is ON when the supply voltage (pulse or DC) exceeds 18V. For this reason the maximum operating supply voltage is 18V.

Figure 33

Figure 34

## Short Circuit (AC and DC conditions)

The TDA2005 can withstand a permanent short-circuit on the output for a supply voltage up to 16V.

## **Polarity Inversion**

High current (up to 10A) can be handled by the device with no damage for a longer period than the blow-out time of a quick 2A fuse (normally connected in series with the supply). This feature is added to avoid destruction, if during fitting to the car, a mistake on the connection of the supply is made.

#### **Open Ground**

When the ratio is in the ON condition and the ground is accidentally opened, a standard audio amplifier will be damaged. On the TDA2005 protection diodes are included to avoid any damage.

#### **Inductive Load**

A protection diode is provided to allow use of the TDA2005 with inductive loads.

## **DC Voltage**

The maximum operating DC voltage for the TDA2005 is 18V.

However the device can withstand a DC voltage up to 28V with no damage. This could occur during winter if two batteries are series connected to crank the engine.

#### Thermal Shut-down

The presence of a thermal limiting circuit offers the following advantages:

- 1) an overload on the output (even if it is permanent), or an excessive ambient temperature can be easily withstood.

- 2) the heatsink can have a smaller factor of safety compared with that of a conventional circuit. There is no device damage in the case of excessive junction temperature: all that happens is that Po (and therefore Ptot) and Id are reduced.

The maximum allowable power dissipation depends upon the size of the external heatsink (i.e. its thermal resistance); Figure 35 shows the dissipable power as a function of ambient temperature for different thermal resistance.

## **Loudspeaker Protection**

The circuit offers loudspeaker protection during short circuit for one wire to ground.

Figure 35: Maximum Allowable Power Dissipation versus Ambient Temperature

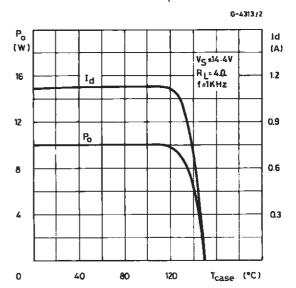

Figure 36: Output Power and Drain Current versus Case Temperature

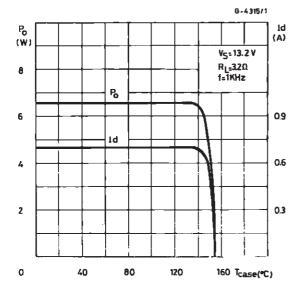

Figure 37: Output Power and Drain Current versus Case Temperature

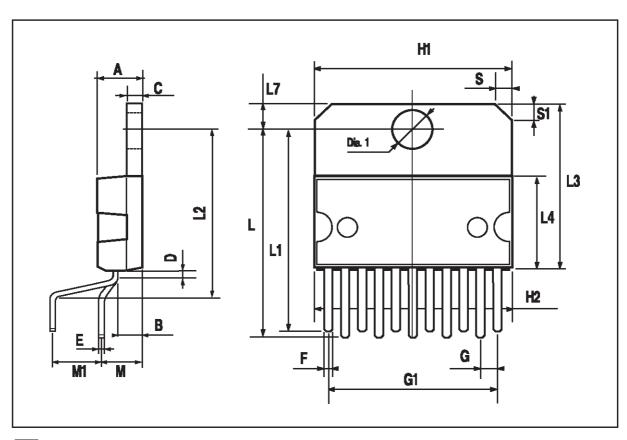

|      |       | mm   |       |       | inch  |       |

|------|-------|------|-------|-------|-------|-------|

| DIM. | MIN.  | TYP. | MAX.  | MIN.  | TYP.  | MAX.  |

| А    |       |      | 5     |       |       | 0.197 |

| В    |       |      | 2.65  |       |       | 0.104 |

| С    |       |      | 1.6   |       |       | 0.063 |

| D    |       | 1    |       |       | 0.039 |       |

| E    | 0.49  |      | 0.55  | 0.019 |       | 0.022 |

| F    | 0.88  |      | 0.95  | 0.035 |       | 0.037 |

| G    | 1.45  | 1.7  | 1.95  | 0.057 | 0.067 | 0.077 |

| G1   | 16.75 | 17   | 17.25 | 0.659 | 0.669 | 0.679 |

| H1   | 19.6  |      |       | 0.772 |       |       |

| H2   |       |      | 20.2  |       |       | 0.795 |

| L    | 21.9  | 22.2 | 22.5  | 0.862 | 0.874 | 0.886 |

| L1   | 21.7  | 22.1 | 22.5  | 0.854 | 0.87  | 0.886 |

| L2   | 17.4  |      | 18.1  | 0.685 |       | 0.713 |

| L3   | 17.25 | 17.5 | 17.75 | 0.679 | 0.689 | 0.699 |

| L4   | 10.3  | 10.7 | 10.9  | 0.406 | 0.421 | 0.429 |

| L7   | 2.65  |      | 2.9   | 0.104 |       | 0.114 |

| М    | 4.25  | 4.55 | 4.85  | 0.167 | 0.179 | 0.191 |

| M1   | 4.73  | 5.08 | 5.43  | 0.186 | 0.200 | 0.214 |

| S    | 1.9   |      | 2.6   | 0.075 |       | 0.102 |

| S1   | 1.9   |      | 2.6   | 0.075 |       | 0.102 |

| Dia1 | 3.65  |      | 3.85  | 0.144 |       | 0.152 |

# OUTLINE AND MECHANICAL DATA

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

# The ST logo is a registered trademark of STMicroelectronics

© 1998 STMicroelectronics – Printed in Italy – All Rights Reserved STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

http://www.st.com