### EN: This Datasheet is presented by the manufacturer.

Please visit our website for pricing and availability at <u>www.hestore.hu</u>.

TEXAS INSTRUMENTS Data sheet acquired from Harris Semiconductor SCHS109

# CD4059A Types

## CMOS Programmable Divide-by-"N" Counter

Standard "A"-Series Types (3-to-15-Volt Rating)

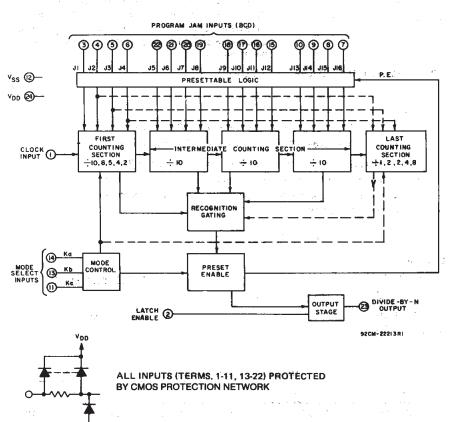

■CD4059 standard "A"-Series types are divide-by-N down-counters that can be programmed to divide an input frequency by any number "N" from 3 to 15,999. The output signal is a pulse one clock-cycle wide occurring at a rate equal to the input frequency divided by N. This single output has TTL drive capability. The down-counter is preset by means of 16 jam inputs.

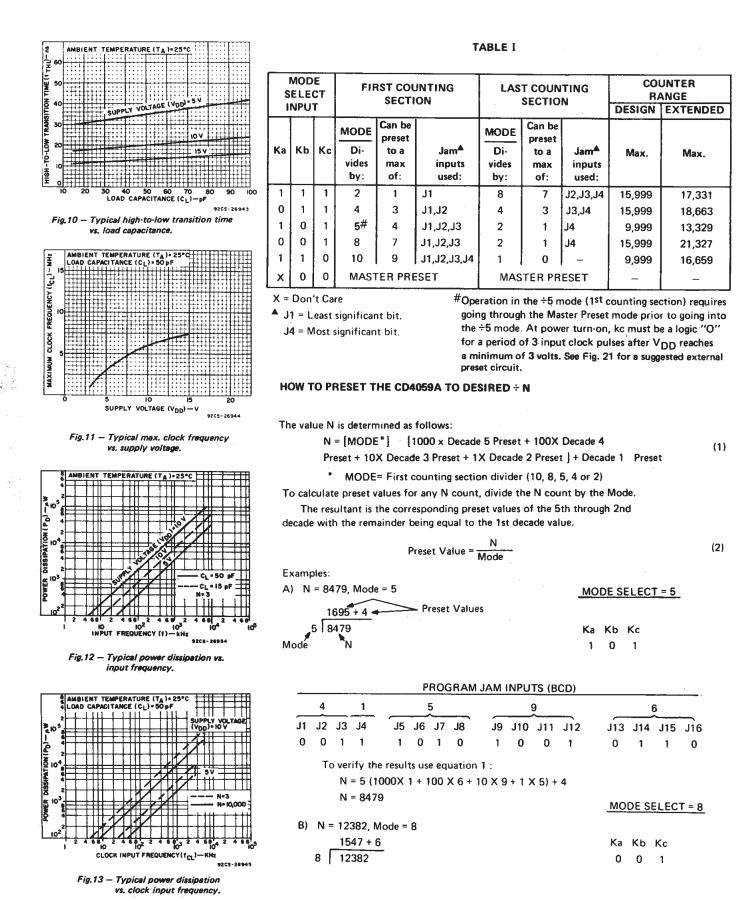

The three Mode-Select Inputs Ka, Kb, and Kc determine the modulus ("divide-by" number) of the first and last counting sections in accordance with the truth table shown in Table I. Every time the first (fastest) counting section goes through one cycle, it reduces by 1 the number that has been preset (jammed) into the three decades of the intermediate counting section and into the last counting section, which consists of flip-flops that are not needed for operating the first counting section. For example, in the ÷ 2 mode, only one flip-flop is needed in the first counting section. Therefore the last counting section has three flip-flops that can be preset to a maximum count of seven with a place value of thousands. If ÷ 10 is desired for the first section, Ka is set to 1, Kb to 1, and Kc to 0. Jam Inputs J1, J2, J3, and J4 are used to preset the first counting section and there is no last counting section. The intermediate counting section consists of three cascaded BCD decade (÷ 10) counters presettable by means of Jam Inputs J5 through J16.

The Mode-Select Inputs permit frequencysynthesizer channel separations of 10, 12.5, 20, 25, or 50 parts. These inputs set the maximum value of N at 9999 (when the first counting section divides by 5 or 10) or 15,999 (when the first counting section divides by 8, 4, or 2).

The three decades of the intermediate counting section can be preset to a binary 15 instead of a binary 9, while their place values are still 1, 10, and 100, multiplied by the number of the  $\div$  N mode. For example, in the  $\div$  8 mode, the number from which counting-down begins can be preset to:

| 3rd decade:           | 1500 |

|-----------------------|------|

| 2nd decade:           | 150  |

| 1st decade:           | 15   |

| Last counting section | 1000 |

The total of these numbers (2665) times 8 equals 21,320. The first counting section can be preset to 7. Therefore, 21,327 is the maximum possible count in the  $\div$  8 mode.

The highest count of the various modes is shown in the column entitled Extended

Counter Range of Table 1. Control inputs Kb and Kc can be used to initiate and lock the counter in the "master preset" state. In this condition the flip-flops in the counter are preset in accordance with the jam inputs and the counter remains in that state as long as Kb and Kc both remain low. The counter begins to count down from the preset state when a counting mode other than the master preset mode is selected.

The counter should always be put in the master preset mode before the  $\div 5$  mode is selected.

Whenever the master preset mode is used, control signals Kb=0 and Kc=0 must be applied for at least 3 full clock pulses.

After the Master Preset Mode inputs have been changed to one of the  $\div$  modes, the next positive-going clock transition changes an internal flip-flop so that the countdown can begin at the second positive-going clock transition. Thus, after an MP (Master Preset) mode, there is always one extra count before the output goes high. Fig.1 illustrates a total count of 3 ( $\div$  8 mode). If the Master Preset mode is started two clock cycles or less before an output pulse, the output pulse will appear at the time due. If the Master Preset Mode is not used the counter jumps back to the "JAM" count when the output pulse appears.

| ᅂᅋᄯᅟᄭᄭ       | MMMM                  | uuu         |

|--------------|-----------------------|-------------|

| Kc (Ka=Kb=O) | 3 2 = 3 3 2 = 3 3 2 = | 3 3 2 - 3 5 |

|              |                       | 9205-2489   |

Fig.1 - Total count of 3.

A "1" on the Latch Enable input will cause the counter output to remain high once an output pulse occurs, and to remain in the high state until the latch input returns to "0". If the Latch Enable is "0", the output pulse will remain high for only 1 cycle of the clock-input signal.

As illustrated in the sample applications, this device is particularly advantageous in communication digital frequency synthesis (VHF, UHF, FM, AM, etc.) where programmable divide-by-"N" counters are an integral part of the synthesizer phase-locked-loop subsystem. The CD4059A can also be used to perform the synthesizer "Fixed Divide-by-R" counting function. It is also useful in generalpurpose counters for instrumentation functions such as totalizers, production counters, and "time out" timers.

**Operational and Performance Features:**

- Synchronous Programmable ÷ N Counter: N = 3 to 9999 or 15,999

- Presettable down-counter

- Fully static operation

- Mode-select control of initial decade counting function (÷ 10,8,5,4,2)

- T<sup>2</sup>L drive capability

- Master preset initialization

- Latchable ÷ N output

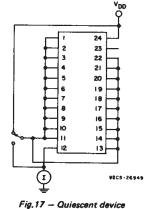

- Quiescent current specified to 15 volts

- Max. input leakage current of 1 µA at 15 volts,full package-temperature range

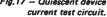

- 1 volt noise margin, full packagetemperature range

- 5-V and 10-V parametric ratings

### Applications

- Communications digital frequency synthesizers: VHF, UHF, FM, AM,etc.

- Fixed or programmable frequency division

- "Time out" timer for consumer-application industrial controls

- Companion Application Note,ICAN-6374, "Application of the CMOS CD4059A Programmable Divide-by-N Counter in FM and Citizens Band Transceiver Digital Tuners"

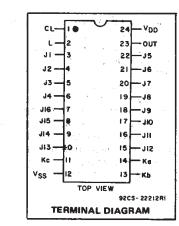

The CD4059A series types are available in a 24-lead ceramic dual-in-line package (D and F suffixes), 24-lead dual-in-line plastic package (E suffix), and in chip form (H suffix).

4

## CD4059A Types

| MAXIMUM RATINGS, Absolute-Maximum Values:                   |                   |

|-------------------------------------------------------------|-------------------|

| DC SUPPLY-VOLTAGE RANGE, (VDD)                              |                   |

| Voltages referenced to V <sub>SS</sub> Terminal)            | 0.5V to +15V      |

| INPUT VOLTAGE RANGE, ALL INPUTS                             | 0.5V to Vpp +0.5V |

| POWER DISSIPATION PER PACKAGE (PD):                         |                   |

| For T <sub>A</sub> = -55°C to +100°C                        |                   |

| For TA = +100°C to +125°C De                                |                   |

| DEVICE DISSIPATION PER OUTPUT TRANSISTOR                    |                   |

| FOR TA = FULL PACKAGE-TEMPERATURE RANGE (All Package Types) | 100mW             |

| OPERATING-TEMPERATURE RANGE (TA)                            |                   |

| STORAGE TEMPERATURE RANGE (Tstg)                            |                   |

| LEAD TEMPERATURE (DURING SOLDERING):                        |                   |

|                                                             | أرياده والمراجع   |

|                                                             |                   |

27 Q. 1. 1. 1.

5

### STATIC ELECTRICAL CHARACTERISTICS

|                  | Conditions         |                   |            | Limits      |          |       |            |          |                   |            |           |

|------------------|--------------------|-------------------|------------|-------------|----------|-------|------------|----------|-------------------|------------|-----------|

| Characteristic   | Vo<br>(V)          | Vin<br>(V)        | VDD<br>(V) | 55°         | -40°     | +85°  | +1250      | <u> </u> | +250              |            | Units     |

|                  | 1.1                | as duran          |            |             | -40-     | TOUT  | T123       | Min.     | Тур.              | Max.       |           |

| Quiescent Device |                    | 1.000             | 5          | 10          | 10       | 700   | 300        |          | 0.02              | 10         | 1         |

| Current,         |                    | 4 H               | 10         | 20          | 20       | 200   | 400        |          | 0.02              | 20         | .μA       |

| JL Max. ⊸ ⊸      | - v.               | $\sigma_{ij} = 1$ | ::15       |             | -        |       |            | -        |                   | 500        | 1. ge     |

| Output Voltage:  | ·. ·               | 200               |            | 1. 20 -     |          | et.   | ÷ 1.       | Ś.,      |                   |            | 1.11      |

| Low Level,       | · j.               | 0,5               | 5          |             |          | .05   | <u> 19</u> | ·        | 0                 | 0.05       | 37        |

| VOL Max.         |                    | 0,10              | 10         |             | <u> </u> | .05   | 12.1       | -        | 0                 | 0.05       | V         |

| High Level,      | (1 <sup>28</sup> ) | 0,5               | 5          |             | 4        | 95    |            | 4.95     | 5                 |            |           |

| VOH Min.         |                    | 0,10              | · 10 ·     |             | 9        | 95    |            | 9.95     | 10                | -          |           |

| Noise Immunity:  |                    |                   |            |             |          | ·     |            |          |                   |            |           |

| Inputs Low,      |                    | 1.1               | 5          | 20 - 1<br>2 |          | .5    |            | 1.5      | 2.25              |            |           |

| VNL Min.         | 2                  | . •               | · 10 ·     |             |          | 3     |            | 3        | 4.5               | _          | v         |

| Inputs High,     |                    |                   | 5          |             |          | .5    |            | 1        | 2.25              | -          | Ť         |

| VNH Min.         |                    |                   | 10         |             |          | 3     |            | 3        | 4.5               | -          |           |

| Noise Margin:    |                    |                   |            |             |          |       | ·· ,       | · · · ·  |                   |            |           |

| Inputs Low,      | 4.5                |                   | 5          |             |          |       | <b>1</b>   |          |                   |            |           |

| VNML Min.        | 9                  |                   | . 10       |             |          |       | 1          |          |                   |            |           |

| Inputs High,     | 0.5                |                   | 5          |             |          |       | 1          |          |                   |            |           |

| VNMH Min.        | 1 <u>:</u>         |                   | 10         |             |          |       | 1 .        | 1        |                   |            |           |

| Output Drive     |                    |                   | · .        |             |          |       |            |          |                   |            |           |

| Current:         |                    |                   |            |             |          |       |            | 1.1.1    |                   |            | 1.1       |

| N-Channel        | 0.4                |                   | 5          | 2,5         | 2.3      | 1.6   | 1.4        | 2        | 4                 | ·          | 1997 - A. |

| (Sink)           | 0.5                |                   | 10         | 5           | 4.7      | 3.3   | 2.8        | 4        | 9                 | -          | - 14 A    |

| IDN Min.         |                    |                   |            |             |          |       | 2.0        | 10       |                   | 1 - 1<br>1 |           |

| P-Channel        |                    |                   |            | -1.3        | -1.15    | -1.6  | -3.2       | -        | mA                |            |           |

| (Source)         | 4.6                |                   | 5          | -0.5        | -0.45    | -0.36 |            | -0.4     | -0.8              | <u> </u>   |           |

| IDP Min.         | 9.5                |                   | 10         | -1.1        | -1       | -0.75 | -0.65      | -0.9     | -1.8              |            |           |

| Input Leakage    |                    |                   |            |             |          |       |            | • 77     | ±10 <sup>-5</sup> |            |           |

| Current:*        |                    |                   | 15         |             | ±1       |       |            |          |                   | ±1         | μA        |

| IIL, IIH Max.    |                    |                   |            | i           |          |       |            |          | 1                 | 1          |           |

\* Any Input

### OPERATING CONDITIONS AT $T_A = 25^{\circ}C$ (Unless otherwise specified)

For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges.

| Characteristic                                        | VDD     | Min.       | Max.     | Units |

|-------------------------------------------------------|---------|------------|----------|-------|

| Supply Voltage<br>Range<br>(over full temp.<br>range) | -       | 3          | 12       | v     |

| Clock Pulse<br>Width                                  | 5<br>10 | 200<br>100 |          | ns    |

| Clock Input<br>Frequency                              | 5<br>10 | -          | 1.5<br>3 | MHz   |

| Clock Input Rise<br>and Fall Time                     | 5<br>10 | -          | 15<br>5  | μs    |

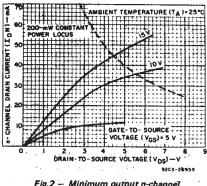

Fig.2 – Minimum output n-channel drain characteristics.

1999

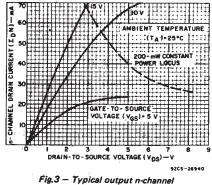

drain characteristics.

2724 C. C. C.

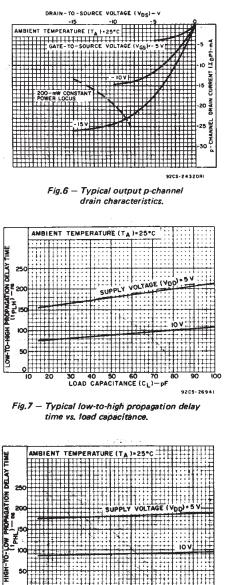

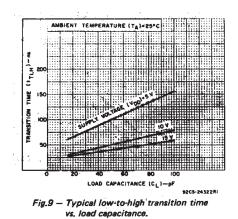

## DYNAMIC ELECTRICAL CHARACTERISTICS AT TA = 25°C, CL = 50 pF, Input tr, tf = 20 ns, RL = 200 kΩ

| CHARACTERISTIC                                           | CONDI-<br>TIONS<br>VDD | ALI   | UNITS |      |                 |  |

|----------------------------------------------------------|------------------------|-------|-------|------|-----------------|--|

| :                                                        | (V)                    | Min.  | Тур.  | Max. | } .             |  |

| Propagation Delay Time: tous: tous                       | .5                     |       | 180   | 360  |                 |  |

| Propagation Delay Time; tpHL, tpLH                       | 10                     | -     | 90    | 180  | ns <sup>:</sup> |  |

| Transition Time:                                         | :                      |       |       | 1    |                 |  |

| 1                                                        | 5                      | · _ · | 35    | 70   | and the second  |  |

| tthr                                                     | 10                     | -     | 20    | 40   | 1               |  |

|                                                          | 5                      |       | 100   | 200  | ns              |  |

| <sup>t</sup> TLH                                         | 10                     | -     | 50    | 100  | 1               |  |

| Maximum Clock Innut Franklinner fr                       | 5                      | 1.5   | 3     | - 1  |                 |  |

| Maximum Clock Input Frequency, fC                        | L 10                   | 3     | 6     | -    | MHz             |  |

| Average Input Capacitance, C <sub>1</sub><br>(any input) |                        | _     | 5     | -    | pF              |  |

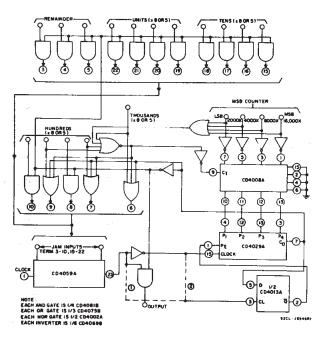

Fig.5 — Functional block diagram.

LOAD CAPACITANCE (CL)-pF 92C5-26942 Fig.8 -- Typical high-to-low propagation delay time vs. load capacitanca.

30 40 50 60 70

4

4-6

| PROGRAM | IΔM | INDUTE |

|---------|-----|--------|

| FRUGRAM | JAW | INFUIS |

|                  |                    | AW SAW INTO IS      | · · · · · · · · · · · · · · · · · · · |

|------------------|--------------------|---------------------|---------------------------------------|

| 6 1              | 7                  | 4                   | 5                                     |

| J1 J2 J3 J4      | J5 J6 J7 J8        | J9 J10 J11 J12      | J13 J14 J15 J16                       |

| 0 1 1 1          | 1 1 1 0            | 0 0 1 0             | 1                                     |

| To verify:       |                    |                     |                                       |

| N = 8 (10        | 00 X 1 + 100 X 5 + | 10 X 4 + 1 X 7) + 6 |                                       |

| N = 1238         | 2 .                | · · ·               |                                       |

|                  |                    |                     | MODE SELECT = 10                      |

| C) N = 8479, Mod | de = 10            |                     |                                       |

| 0847 + 9         |                    |                     | Ka Kb Kc                              |

| 10 8479          |                    |                     | 1 1 <b>0</b>                          |

|                  | PROGRA             | M JAM INPUTS        |                                       |

| _  |    | 9   |                  | 7           |              |     | 4   |       |      | 8     |     |     |     |      |                |

|----|----|-----|------------------|-------------|--------------|-----|-----|-------|------|-------|-----|-----|-----|------|----------------|

| J1 | J2 | J3  | J4 Ì             | J5          | - <b>J</b> 6 | J7  | ງ8ີ | . ja  | J10  | J11   | J12 | J13 | J14 | J15  | J16            |

| 1  | 0  | 0   | 1                | 1           | 1            | 1   | 0   | 0     | 0    | 1     | 0   | 0   | 0   | 0    | <sup>`</sup> 1 |

|    | Τc | Ver | •                |             |              | 100 |     |       |      | N -11 |     |     |     |      |                |

|    |    |     | = 10 (<br>= 8479 | 1000 X<br>) |              | 100 | 7 8 | + 100 | (4+) | X /)  | + 9 |     |     | ** . |                |

n sen l'arre à àstre de la company de la No company de la company de

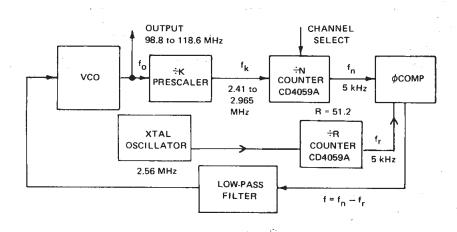

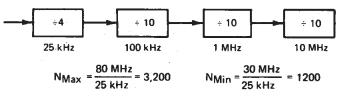

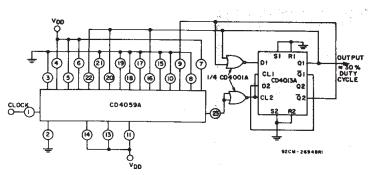

DIGITAL PHASE-LOCKED LOOP (PLL) FOR FM BAND SYNTHESIZER

1) Calculating Min & Max "N" Values :

Output Freq. Range  $(\tau_0) = 98.8$  to 118.6 MHz Channel Spacing Freq.  $(f_c) = 200$  kHz Division Factor (k) = 40

Reference Freq. (fr) =

$$\frac{f_c}{k} = \frac{200}{40}$$

kHz = 5 kHz

$$f_{k} = \frac{f_{0}}{40}$$

:  $f_{k}Max. = \frac{118.6 \text{ MHz}}{40} = 2.965 \text{ MHz}; f_{k}Min = \frac{98.8 \text{ MHz}}{40} = 2.47 \text{ MHz}$

$\therefore N = \frac{f_{0}}{f_{C}}$

$$N_{Max} = \frac{118.6 \text{ MHz}}{200 \text{ kHz}} = 593$$

$N_{Min} = \frac{98.8 \text{ MHz}}{200 \text{ kHz}} = 494$   $R = \frac{2.56 \text{ MHz}}{5 \text{ kHz}} = 512$

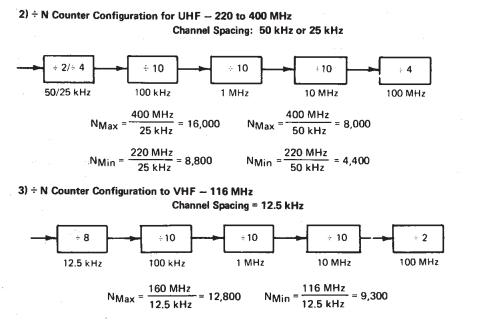

### "CASCADING" VIA OTHER COUNTERS

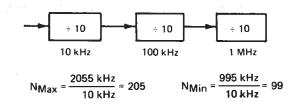

Fig. 14 shows a BCD-switch compatible arrangement suitable for  $\div$  8 and  $\div$  5 modes. which can be adapted, with slight changes, to the other divide-by-modes. In order to be able to preset to any number from three to about 256,000, while preserving the BCDswitch compatible character of the jam inputs, a rather complex cascading scheme is required. Such a cascading scheme is necessary because the CD4059A can never be preset to a count less than 3 and logic is needed to detect the condition that one of the numbers to be preset in the CD4059A is rather small. In order to simplify the detection logic, only that condition is detected where the jam inputs to terminals 6, 7, and 9 would be low during one count. If such a condition is detected, and if at least 1 is expected to be jammed into the MSB counter, the detection logic removes one from the number to be jammed into the MSB counter (with a place

forcing terminals 6, 7, and 9 high. The clock of the CD4013A may be driven directly from the output of the CD4059A, as shown by dashed aption. (1), or by the inverted output of the CD4059A, option (2). If option (2) is used the CD4029A cannot count cycles shorter than 3. If option (1) is used propagation delay problems may occur at high counting speeds.

value of 2000 times the divide-by-mode) and jams the same 2000 into the CD4059A by

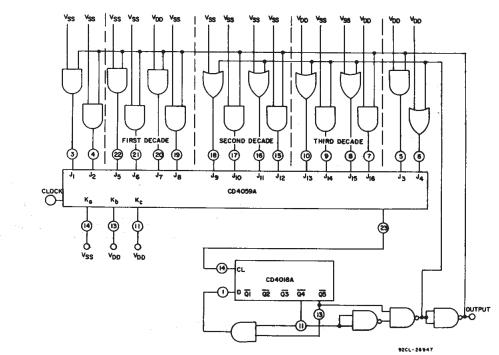

The general circuit in Fig.14 can be simplified considerably if the range of the cascaded counters does not have to start at a very low value. Fig.15 shows an arrangement in the  $\div$  4 mode, where the counting range extends in a BCD-switch compatible manner from 88,003 to 103,999. The arrangement shown in Fig.15 is easy to follow; once during each cycle, the less significant digits are jammed in (14,712 in this case) and then 11,000 (4 x 2750) is jammed in eight times in succession, by forcing jam inputs high or low, as required.

Numbers larger than the extended counter range can also be produced by cascading the CD4059A with some other counting device. Fig.16 shows such an arrangement where only one fixed divide-by number is desired which is close to three times the extended counter range as shown in the last column of Table I. The dual flip-flop wired to produce a ÷ 3 count, can be replaced by other counters such as the CD4029, CD4510, CD4516, CD4017, or the CD4022. In Fig.16 the ÷ N subsystem is preset once to a number smaller than the desired divide-by number. This smaller number represents the less significant digits of the divide-by number. The subsystem is then preset one or more times to a round number (e.g. 1000, 2000) and multiplied by the number of the divide-by mode (÷ 2 in the example of Fig.16). It is important that the second counting device has an output that is high or low, as the case may be, during only one of its counting states.

4

## CD4059A Types

Fig.14 - BCD switch-compatible : N system of the most general kind.

Fig. 15 - Dividing by any number from 88,003 to 103,999.

Fig. 16 - Division by 47,690 in ÷2 mode.

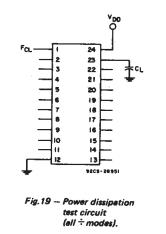

test circuit.

autoraa Arto

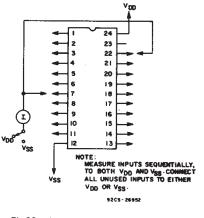

Fig.20 - Input leakage current test circuit.

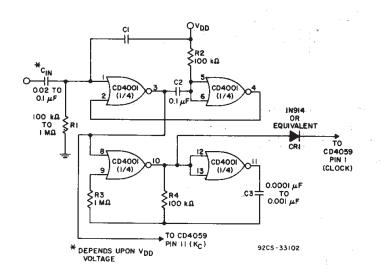

For changing from any mode other than mode 5 (with power on), apply positive pulse to C<sub>in</sub>. This circuit automatically selects master preset mode (K<sub>b</sub> = 0, K<sub>c</sub> = 0) before going into the select conditions for mode 5 (K<sub>a</sub> = 1, K<sub>b</sub> = 0, K = 1). The selection of C<sub>1</sub> and C<sub>2</sub> is critical. C<sub>1</sub> is determined by the VDD voltage--the lower VDD's need larger C<sub>1</sub>'s. C<sub>2</sub> must be 0.1  $\mu$ F or larger.

### Fig.21 - CD4059A mode 5 power on master preset circuit.

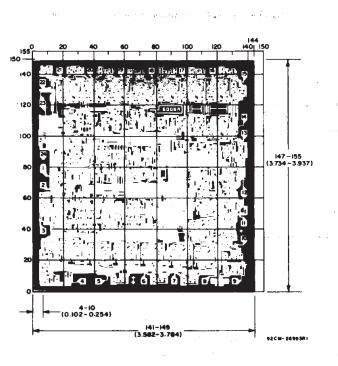

Dimensions in parentheses are in millimeters and are derived from the basic inch dimensions as indicated. Grid graduations are in mils ( $10^{-3}$  inch).

Dimensions and pad layout for CD4059AH.

#### un an trainn an trainn an trainn an trainn 1a**Grte**r (al an trainn an trainn an trainn an trainn an trainn 1a fall an trainn an trainn an trainn an trainn

e e anter a construction de la const

4-10

### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated